Heterogeneous Embedded Computer Architectures and Programming Paradigms for Enabling Internet of Things (IoT)

# Charles Liu, Ph.D.,

Professor,

CAL STATE

Department of Electrical Engineering and Computer Engineering California State University, Los Angeles

# cliu@calstatela.edu

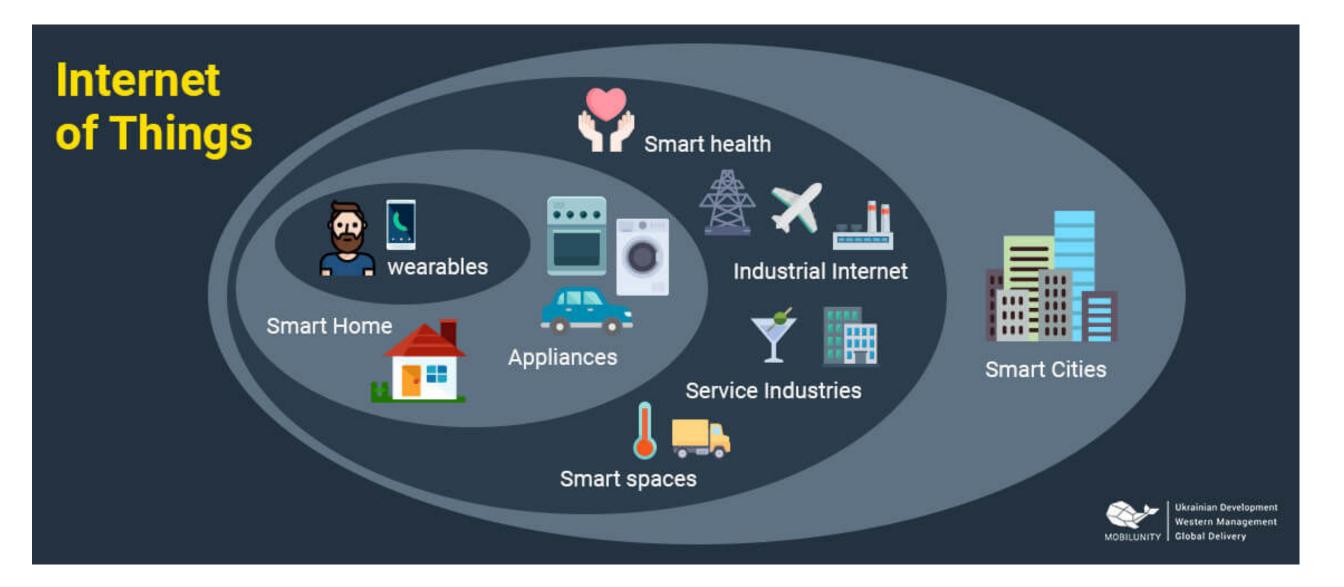

From <<u>https://mobilunity.com/blog/iot-developer-salary-rates/</u>>

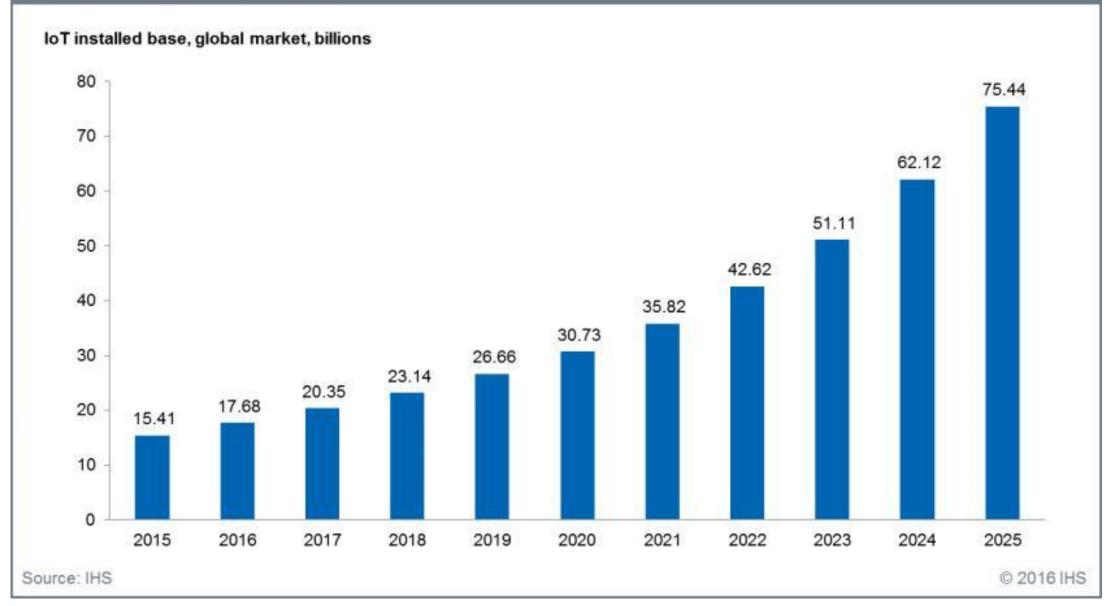

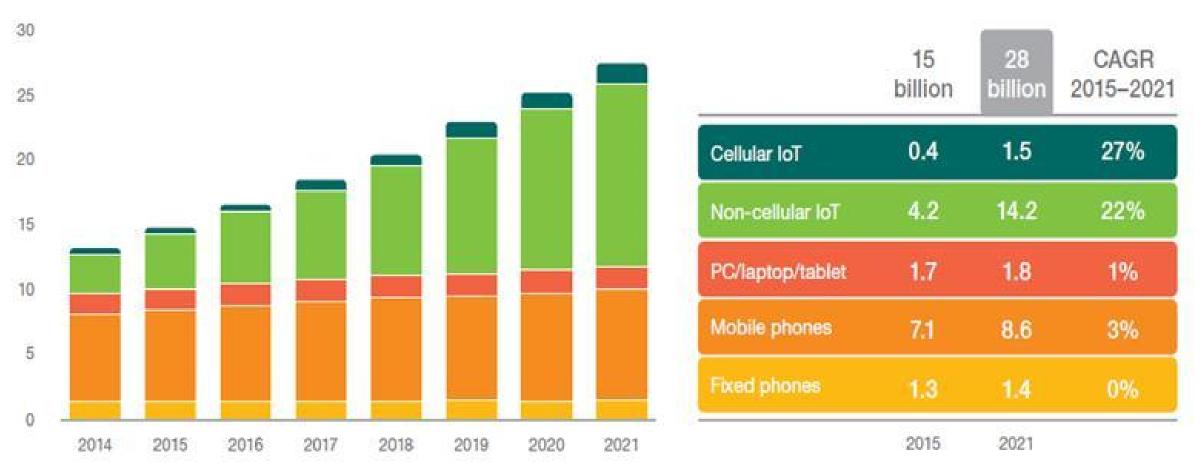

#### Figure 1. The IoT market will be massive

From <<u>https://blogs-images.forbes.com/louiscolumbus/files/2016/11/IHS.jpg</u>>

# THE INTERNET OF THINGS

Connected devices (billions)

From <<u>https://blogs-images.forbes.com/louiscolumbus/files/2016/07/Internet-of-Things-Forecast.jpg</u>>

From < https://www.qualcomm.com/news/onq/2017/08/16/we-are-making-device-ai-ubiquitous >

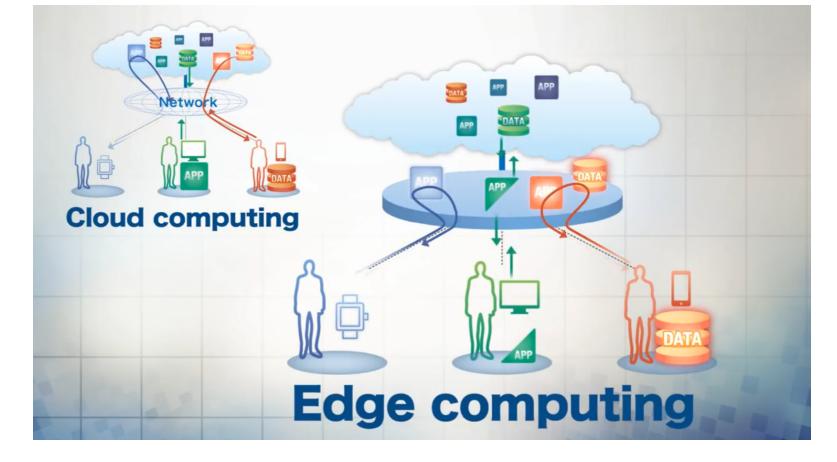

# **Edge Computing**

The ability to do advanced on-device processing and analytics is referred to as "edge computing." *Edge computing is a counterpart to the cloud computing*

Edge computing provides new possibilities in IoT applications,

machine learning for tasks such as object detection, face recognition, language processing, and obstacle

avoidance

Instead of sending streams of images/videos to the cloud for processing, in-situ pre-processing is performed

Advantages: Saving in network and computing resources, reducing latency, improving security and privacy (personally identifiable information vs. demographic information)

[E.g.] Proactive in-car service - natural language interface using Edge computing allows smart speakers to react more quickly by interpreting voice instructions locally. Heterogeneous computer architectures are adopted for edge computing - integrating diverse engines such as CPUs, GPUs and DSPs — in IoT devices so that different workloads are assigned to the most efficient compute engine, thus improving performance and power efficiency.

[E.g.] The Hexagon DSP with Qualcomm Hexagon Vector eXtensions on Snapdragon 835 has been shown to offer a 25X improvement in energy efficiency and an 8X improvement in performance when compared against running the same workloads (GoogleNet Inception Network) on the Qualcomm Kryo CPU.

From <<u>https://www.qualcomm.com/news/onq/2017/08/16/we-are-making-device-ai-ubiquitous</u>>

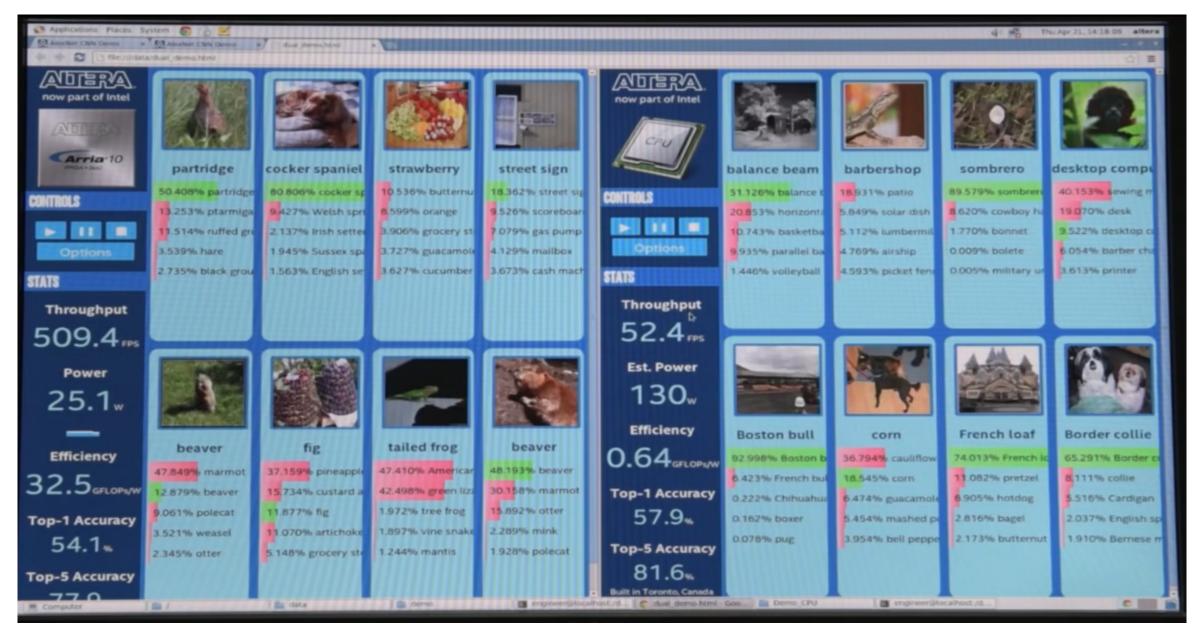

#### Convolutional Neural Network CNN Implementation on Altera FPGA using OpenCL

https://www.youtube.com/watch?v=78Qd5t-Mn0s

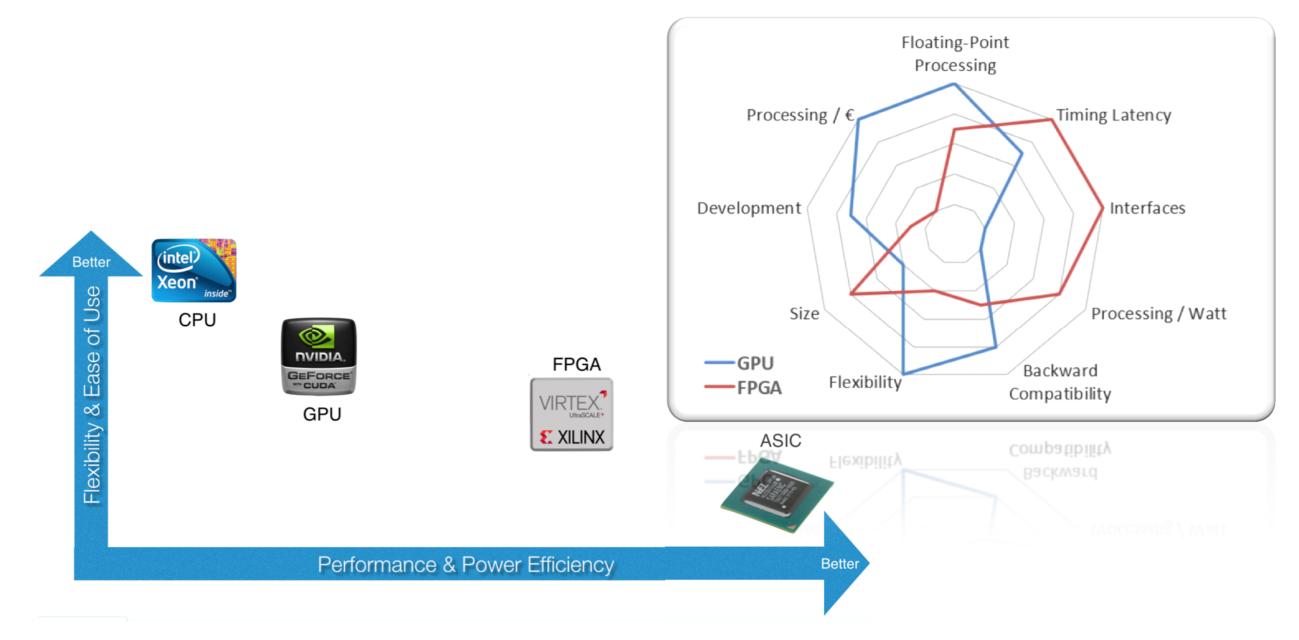

# Heterogeneous Computer Architectures

- CPUs

- GPUs

- Vector Processors

- Image/Signal Processors

- FPGAs

Suppose you want to add two vectors of numbers. There are many ways to spell this – programming paradigms.

C uses a loop spelling

Matlab uses a vector spelling

for(i=0;i<n;++i) a[i]=b[i]+c[i];

a=b+c;

```

SIMD uses a "short vector" spelling

```

SIMT uses a "scalar" spelling

```

void add(uint32_t *a, uint32_t *b, uint32_t *c,

int n) {

```

```

for(int i=0; i<n; i+=4) {

//compute c[i], c[i+1], c[i+2], c[i+3]</pre>

```

}

```

uint32x4_t b4 = vld1q_u32(b+i);

uint32x4_t c4 = vld1q_u32(c+i);

uint32x4_t a4 = vaddq_u32(b4,c4);

vst1q_u32(a+i,a4);

```

```

__global__ void

add(float *a, float *b, float *c) {

int i = blockIdx.x * blockDim.x +

threadIdx.x;

```

```

a[i]=b[i]+c[i]; //no loop!

}

```

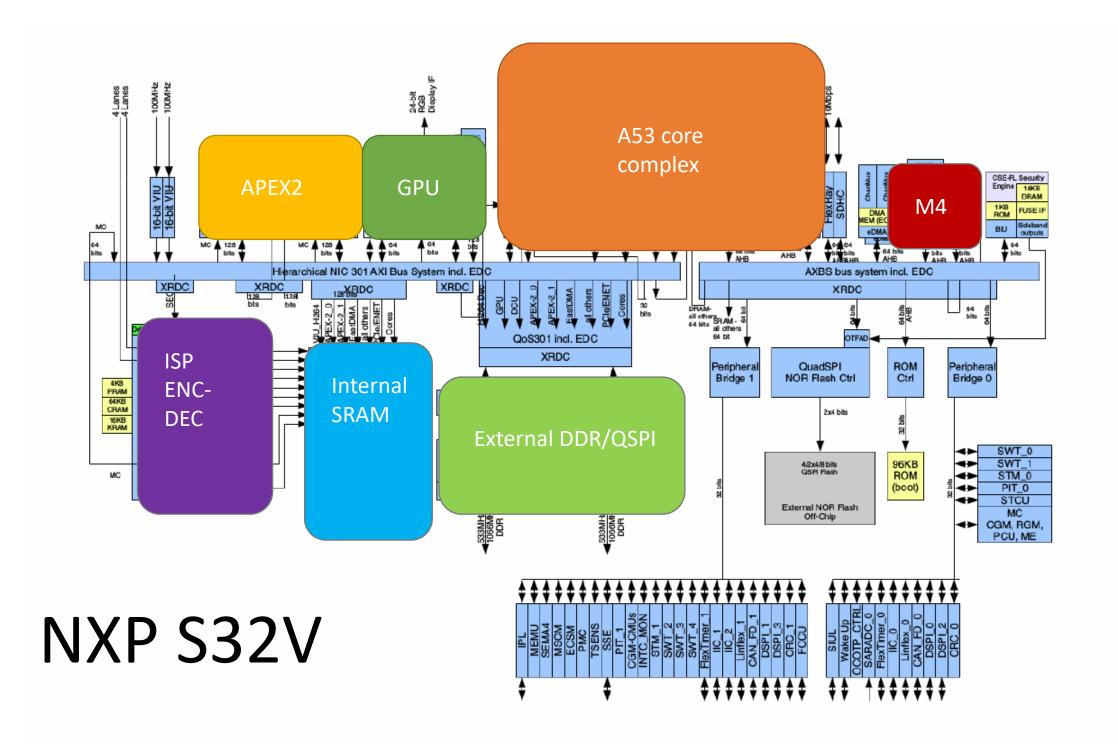

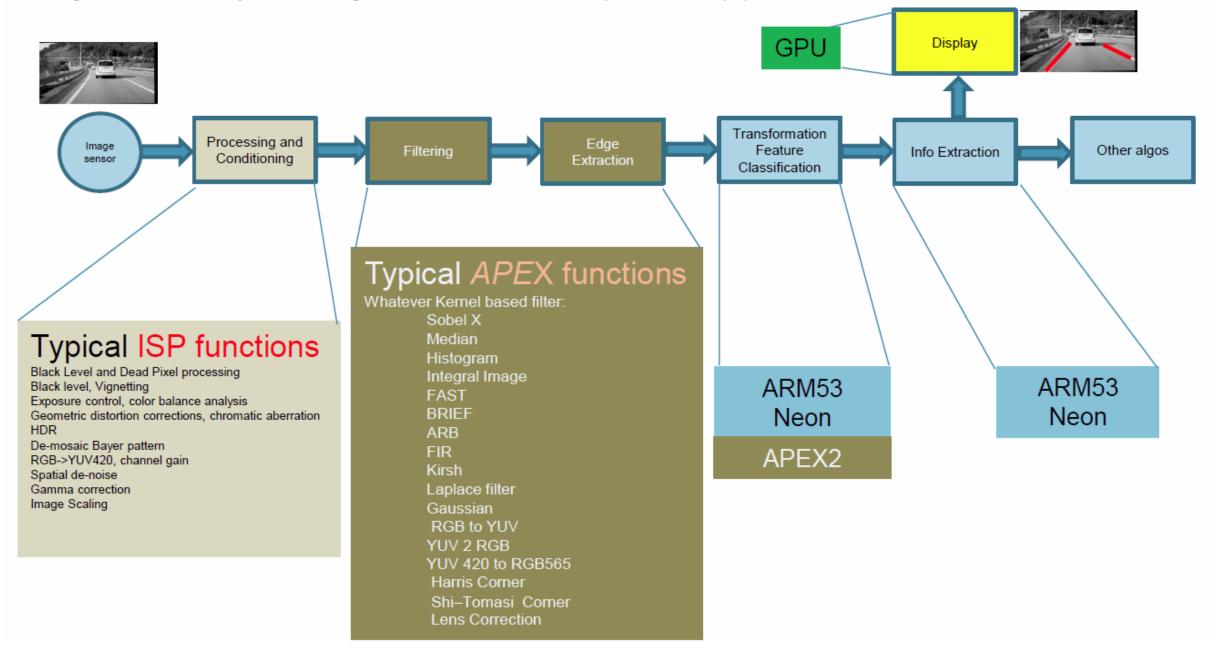

Each engine has a best efficiency on certain type of functions. To let the complete system working at highest efficiency each engine needs to work in parallel in pipeline mode.

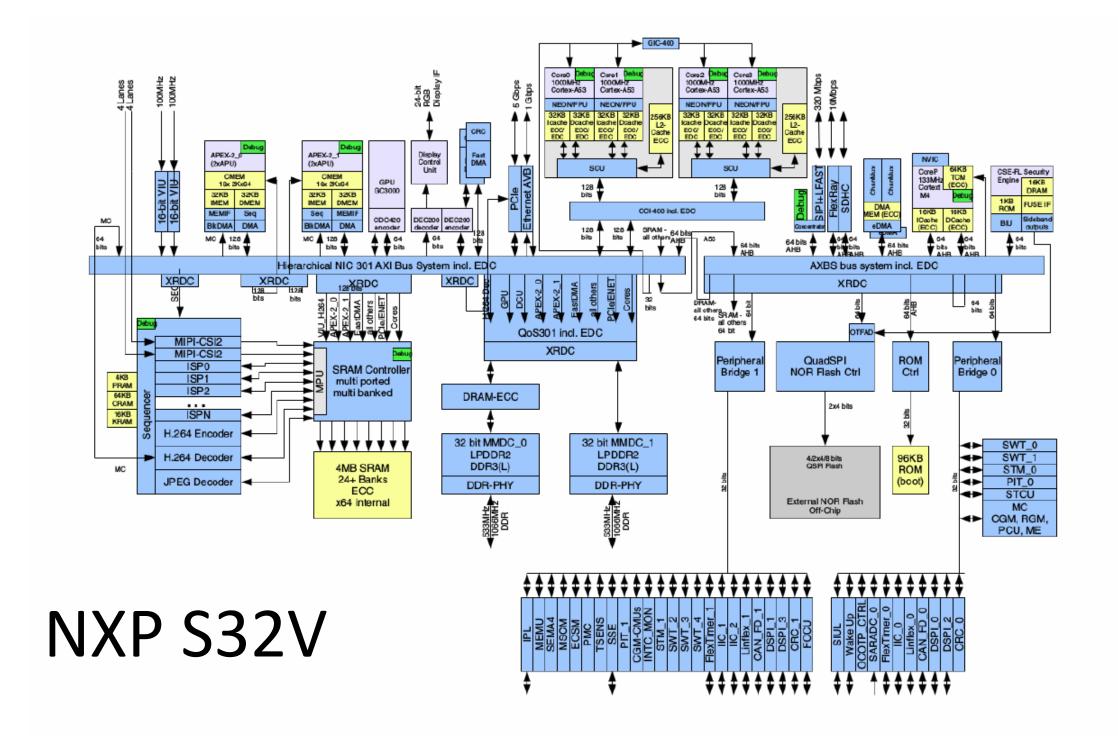

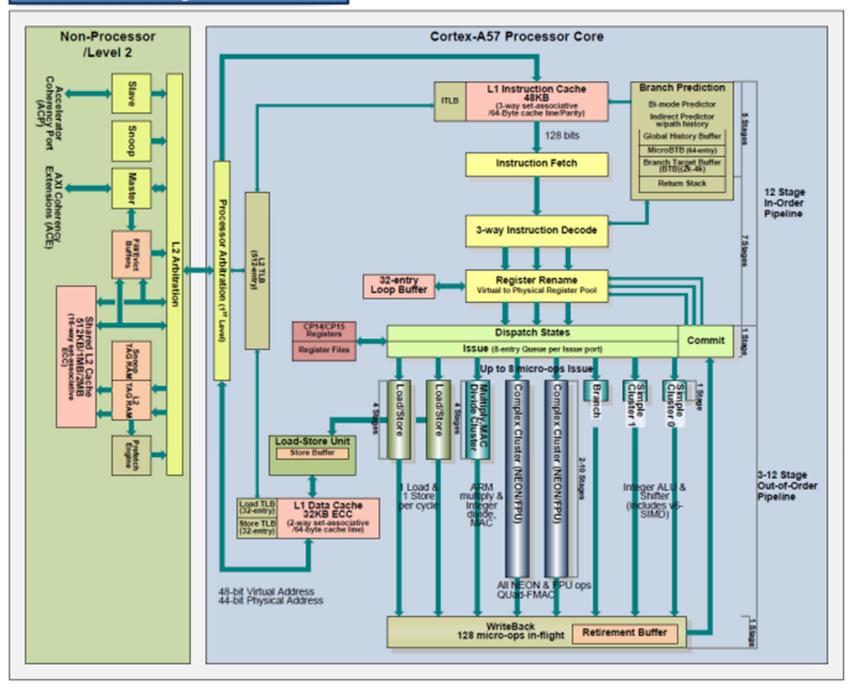

#### ARM Cortex-A57 Block Diagram

## Programming Paradigms

|                               | OpenACC                                                                        | OpenMP                                                                                                     | OpenCL                                                                             | CUDA                                                                           |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Parallelism                   | - data paral-<br>lelism<br>- asynchronous<br>task parallelism<br>- device only | - data paral-<br>lelism<br>- asynchronous<br>task parallelism<br>- host and device                         | - data paral-<br>lelism<br>- asynchronous<br>task parallelism<br>- host and device | - data paral-<br>lelism<br>- asynchronous<br>task parallelism<br>- device only |  |  |  |

| Architecture<br>abstraction   | - memory hierar-<br>chy<br>- explicit data<br>mapping and<br>movement          | - memory hier-<br>archy - data and<br>computation<br>binding<br>- explicit data<br>mapping and<br>movement | - memory hierar-<br>chy<br>- explicit data<br>mapping and<br>movement              | - memory hierar-<br>chy<br>- explicit data<br>mapping and<br>movement          |  |  |  |

| Synchroni-<br>zation          | - reduction<br>- join                                                          | - barrier<br>- reduction<br>- join                                                                         | - barrier;<br>- reduction                                                          | - barrier                                                                      |  |  |  |

| Framework im-<br>plementation | compiler directives<br>for $C/C++$ and<br>Fortran                              | *                                                                                                          | C/C++ extension                                                                    | C/C++ extension                                                                |  |  |  |

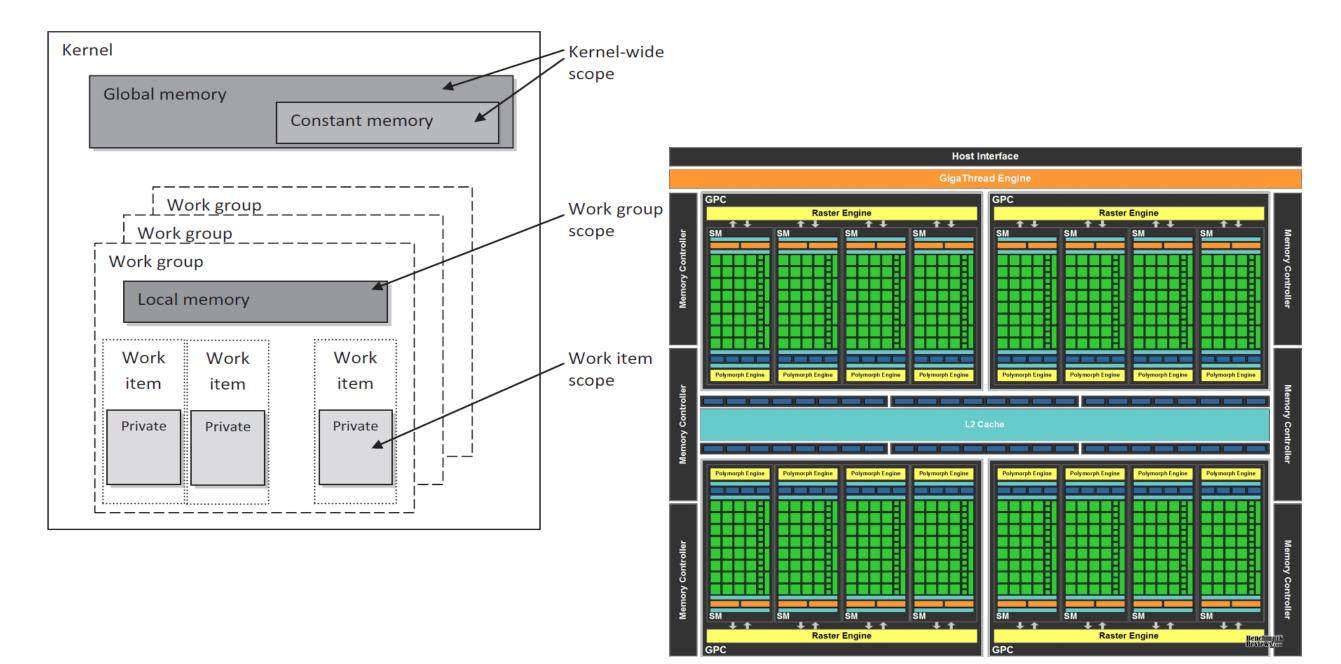

#### NVIDIA GUP: GeForce\_GTX\_480\_Fermi - Single Instruction Multiple Thread (SIMT) architecture

https://www.techpowerup.com/reviews/NVIDIA/GeForce\_GTX\_480\_Fermi/

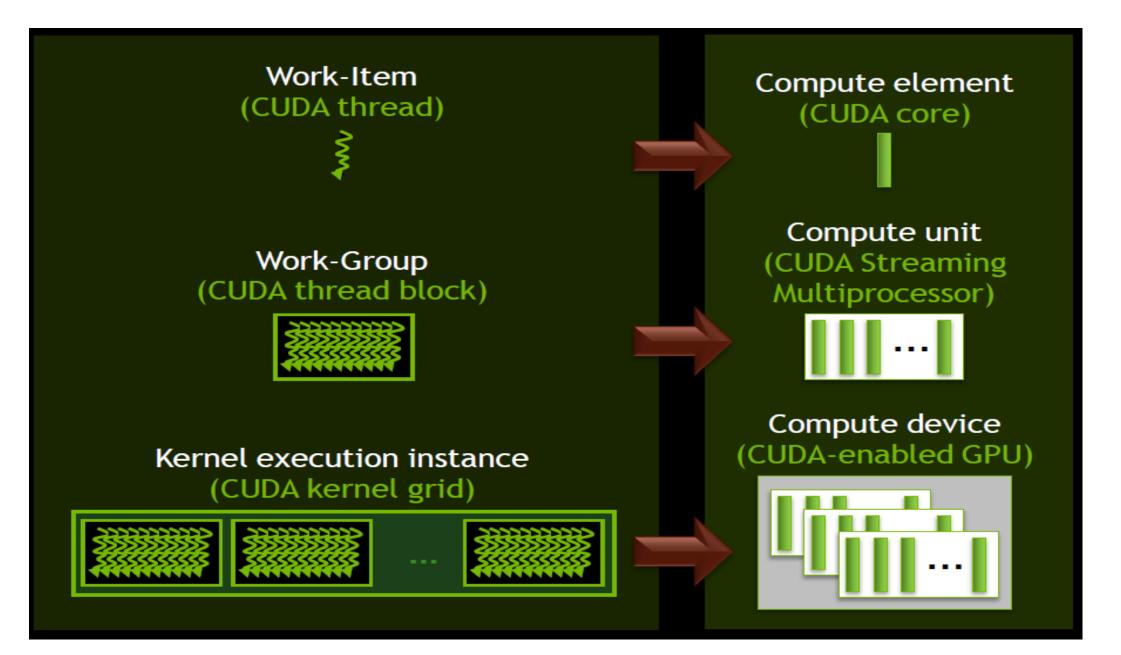

CUDA and OpenCL terminology correspondence.

The SMs schedule and execute threads in lockstep groups of 32 threads called *warps*.

| Warp Scheduler                                 | Warp Scheduler                                 |

|------------------------------------------------|------------------------------------------------|

| Instruction Dispatch Unit                      | Instruction Dispatch Unit                      |

|                                                |                                                |

| Warp 8 instruction 11<br>Warp 2 instruction 42 | Warp 9 instruction 11<br>Warp 3 instruction 33 |

| Warp 14 instruction 95                         | Warp 15 instruction 95                         |

|                                                |                                                |

| Warp 8 instruction 12                          | Warp 9 instruction 12                          |

| Warp 14 instruction 96                         | Warp 3 instruction 34                          |

| Warp 2 instruction 43                          | Warp 15 instruction 96                         |

time

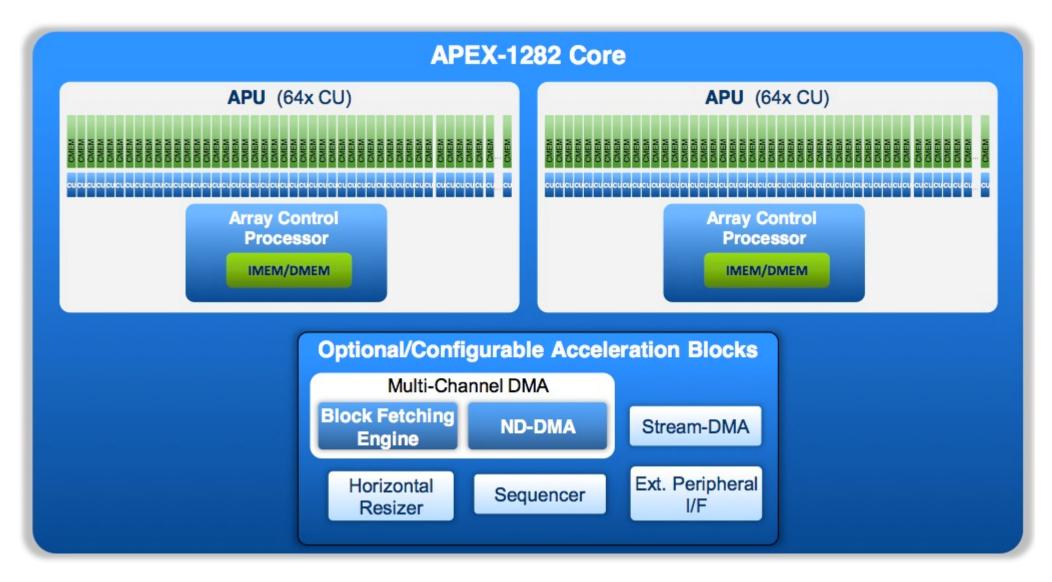

#### **CogniVue's APEX vision processor core architectures**

https://www.bdti.com/InsideDSP/2015/06/30/CogniVue

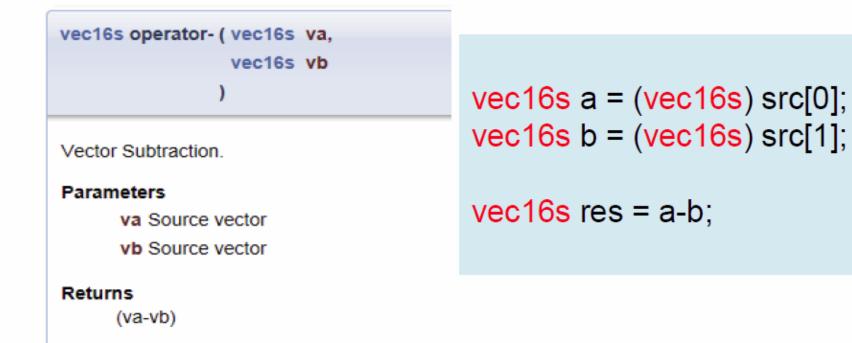

## Example vector operator -

|     | CU0 | CU1 | CU2 | CU3 | CU4        | CU5 | CU6 | CU7 | CU8 | CU9 ( | CU10 | CU11 | CU12 | CU13 ( | CU14 | CU15 | CU16 | CU17 | CU18 ( | CU19 | CU20 | CU21 | CU22 | CU23 | CU24 | CU25 | CU26 | CU27 | CU28 | CU29 | CU30 | CU31 |     |

|-----|-----|-----|-----|-----|------------|-----|-----|-----|-----|-------|------|------|------|--------|------|------|------|------|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|

| 0   | C9  | 9E  | 9C  | A C | <b>6</b> B | 6C  | 6C  | 77  | 85  | 82    | 85   | 85   | 86   | 87     | 84   | 85   | 8A   | 82   | 83     | 7D   | 6A   | 9F   | 9C   | 99   | 9B   | 9F   | D7   | 6E   | 7B   | 7C   | 7C   | 73   | 2   |

| 1   | 00  | 00  | 00  | 00  | 00         | 00  | 00  | 00  | 00  | 00    | 00   | 00   | 00   | 00     | 00   | 00   | 00   | 00   | 00     | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | a   |

| 2   |     |     |     |     |            |     |     |     |     |       |      |      |      |        |      |      |      |      |        |      |      |      |      |      |      |      |      |      |      |      |      |      | [   |

| 3   | A 3 | 9D  | 9D  | ΑB  | 5D         | 6A  | 6B  | 7A  | 84  | 80    | 86   | 85   | 87   | 86     | 85   | 86   | 87   | 81   | 83     | 7A   | 74   | A 2  | 9F   | 99   | 9D   | B2   | C7   | 77   | 7A   | 7D   | 7D   | 6D   | h   |

| - 4 | 00  | 00  | 00  | 00  | 00         | 00  | 00  | 00  | 00  | 00    | 00   | 00   | 00   | 00     | 00   | 00   | 00   | 00   | 00     | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 00   | 5   |

| 5   |     |     |     |     |            |     |     |     |     |       |      |      |      |        |      |      |      |      |        |      |      |      |      |      |      |      |      |      |      |      |      |      | [   |

| 6   | 6C  | 3B  | 39  | 57  | C8         | D6  | D7  | F1  | 09  | 02    | 0B   | 0A   | 0D   | 0D     | 09   | 0B   | 11   | 03   | 06     | F7   | DE   | 41   | 3B   | 32   | 38   | 51   | 9E   | E5   | F5   | F9   | F9   | E0   | res |

| 7   | 01  | 01  | 01  | 01  | 00         | 00  | 00  | 00  | 01  | 01    | 01   | 01   | 01   | 01     | 01   | 01   | 01   | 01   | 01     | 00   | 00   | 01   | 01   | 01   | 01   | 01   | 01   | 00   | 00   | 00   | 00   | 00   | 165 |

# **Understand vif**

```

vec08u V0,V1;

vec16u VR;

vif (V0 < V1) // condition

{

VR = V0 + V1; // TRUE

}

velse

{

VR = V0; // FALSE

}

vendif

```

# CMEM final after executing the velse statement and the second predicated instruction.

| CU0 | CU1 | CU2 | CU3 | CU4 | CU5 | CU6 | CU7 | CU8 | CU9   | CU10   | CU11 | CU12 | CU13 ( | CU14   | CU15 | CU16 | CU17   | CU18 ( | CU19 | CU20 | CU21 | CU22 | CU23 | CU24 | CU25 | CU26      | CU27 | CU28 | CU29 | CU30 | CU31 |           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|--------|------|------|--------|--------|------|------|--------|--------|------|------|------|------|------|------|------|-----------|------|------|------|------|------|-----------|

| 0   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 0   | 0     | 1      | 0    | 1    | 0      | 1      | 1    | 0    | 0      | 0      | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0         | 1    | 0    | 1    | 1    | 0    | register  |

| CUO | CU1 | CU2 | CU3 | CU4 | CU5 | CU6 | CU7 | CU8 | CU9 ( | CU10 ( | :011 | CU12 | CU13 ( | :U14 ( | CU15 | CU16 | CU17 ( | :U18 ( | CU19 | CU20 | CU21 | CU22 | CU23 | CU24 | CU25 | CU26      | CU27 | CU28 | CU29 | CU30 | CU31 |           |

| C9  | 9E  | 9C  | AC  | 6B  | 6C  | 6C  | 77  | 85  | 82    | 85     | 85   | 86   | 87     | 84     | 85   | 8A   | 82     | 83     | 7D   | 6A   | 9F   | 9C   | 99   | 9B   | 9F   | D7        | 6E   | 7B   | 7C   | 7C   | 73   | <b>V0</b> |

| A3  | 9D  | 9D  | AB  | 5D  | 6A  | 6B  | 7A  | 84  | 80    | 86     | 85   | 87   | 86     | 85     | 86   | 87   | 81     | 83     | 7A   | 74   | A2   | 9F   | 99   | 9D   | B2   | <b>C7</b> | 77   | 7A   | 7D   | 7D   | 6D   | V1        |

|     |     |     |     |     |     |     |     |     |       |        |      |      |        |        |      |      |        |        |      |      |      |      |      |      |      |           |      |      |      |      |      |           |

| C9  | 9E  | 39  | AC  | 6B  | 6C  | 6C  | F1  | 85  | 82    | 0B     | 85   | 0D   | 87     | 09     | 0B   | 8A   | 82     | 83     | 7D   | DE   | 41   | 3B   | 99   | 38   | 51   | D7        | E5   | 7B   | F9   | F9   | 73   | VR        |

| 00  | 00  | 01  | 00  | 00  | 00  | 00  | 00  | 00  | 00    | 01     | 00   | 01   | 00     | 01     | 01   | 00   | 00     | 00     | 00   | 00   | 01   | 01   | 00   | 01   | 01   | 00        | 00   | 00   | 00   | 00   | 00   |           |

|     |     |     |     |     |     |     |     |     |       |        |      |      |        |        |      |      |        |        |      |      |      |      |      |      |      |           |      |      |      |      |      |           |

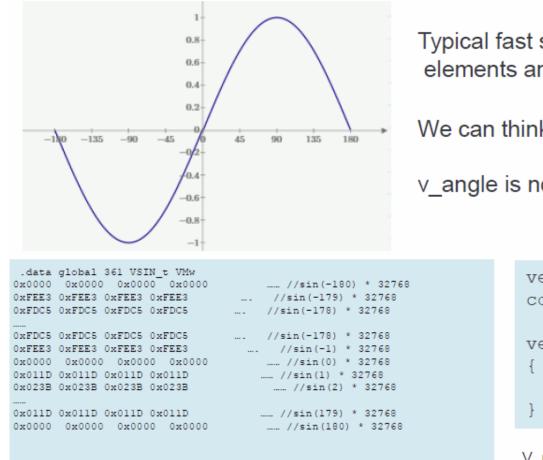

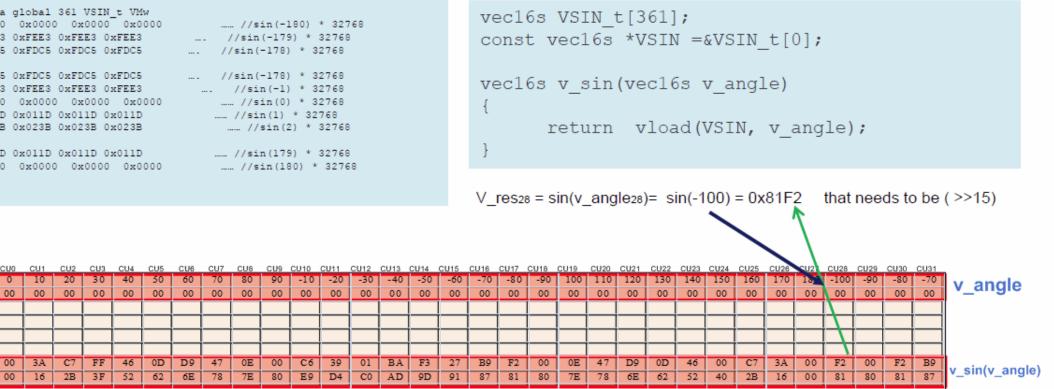

### vload example; vsin

2B 3F

6E

Typical fast sin can be build with a look-up table with 361 elements and use the angle as the table index

We can think to build the vector vsin in the same way.

v angle is now a vector and vsin(v angle) returns a vector with

$res{i} = sin(v_angle{i})$

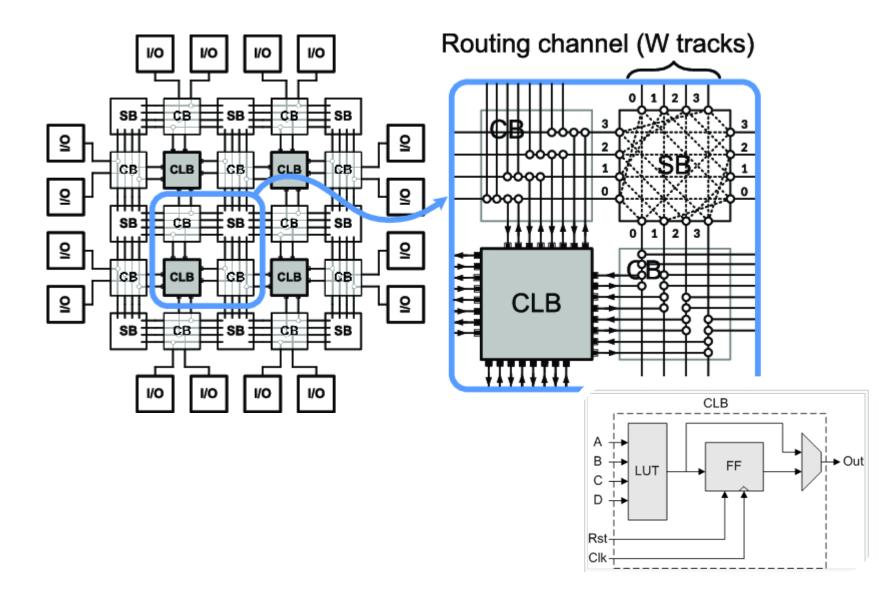

# Field programmable Gate Array (FPGA) is another Choice!

Island-style global FPGA architecture. A unit tile consists of Configurable Logic Block (CLB), Connect Box (CB) and Switch Box(SB).

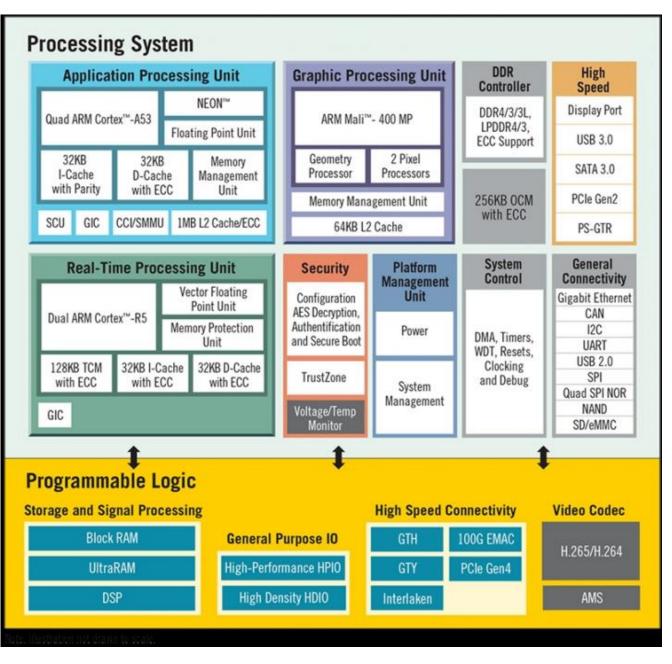

#### Heterogeneous MPSoC Xilinx

#### Xilinx's 16nm UltraScale+

# SoC Design Challenges

Verification **IP** Quality Deep submicron effects **Test Methodology** IP verification Integration IP Updates **Testing equipment Limitations** Architecture Advance Process **Simulation Models** Tools **IP** Completeness IP reuse system partitioning Power Management Time to Market

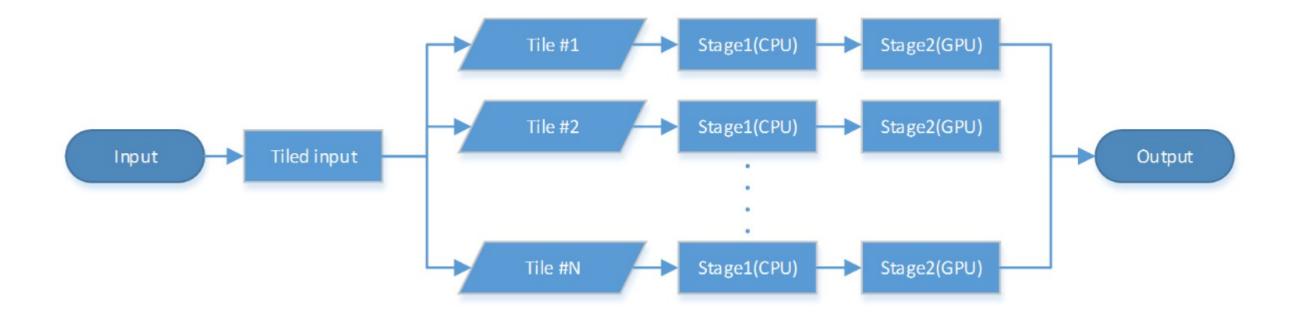

# Data streaming

General algorithm execution model

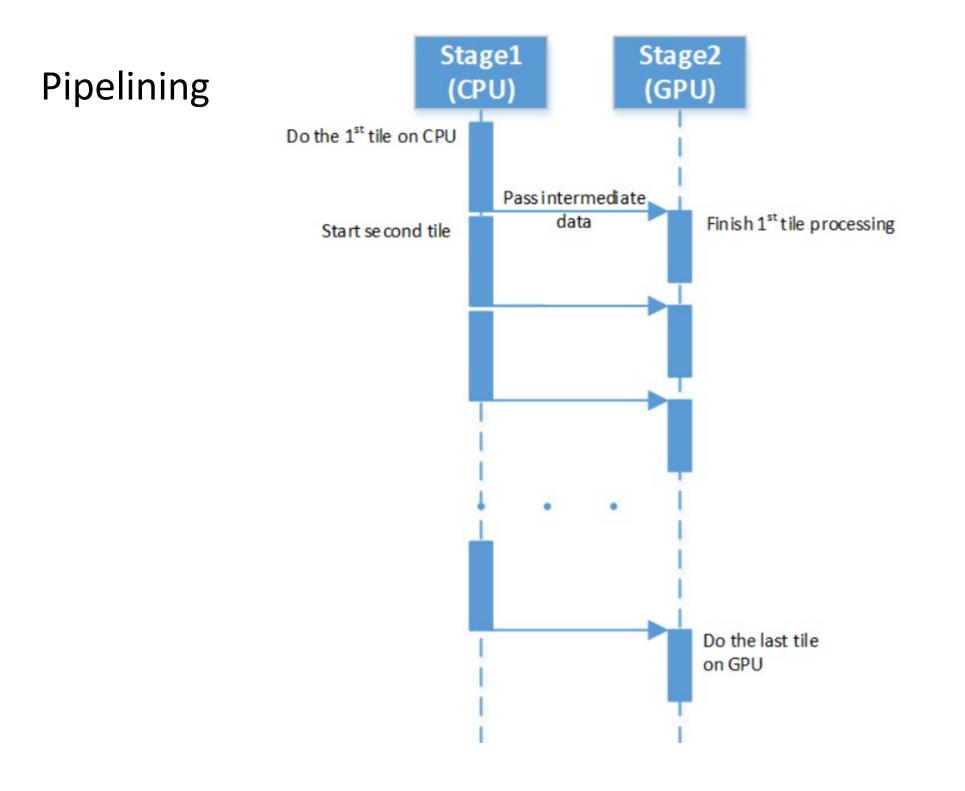

# Pipelining

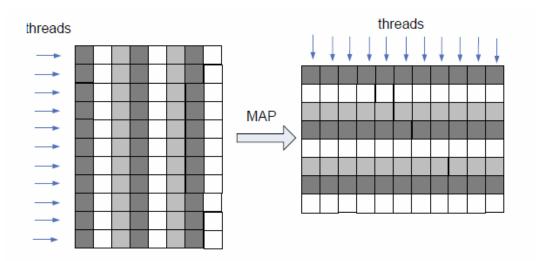

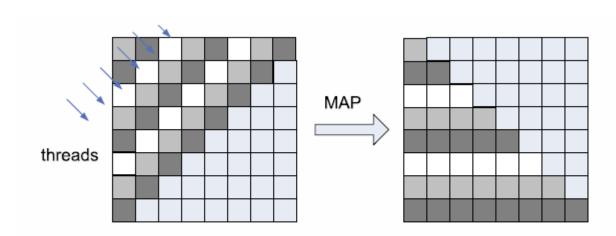

# Data Mapping and Remapping

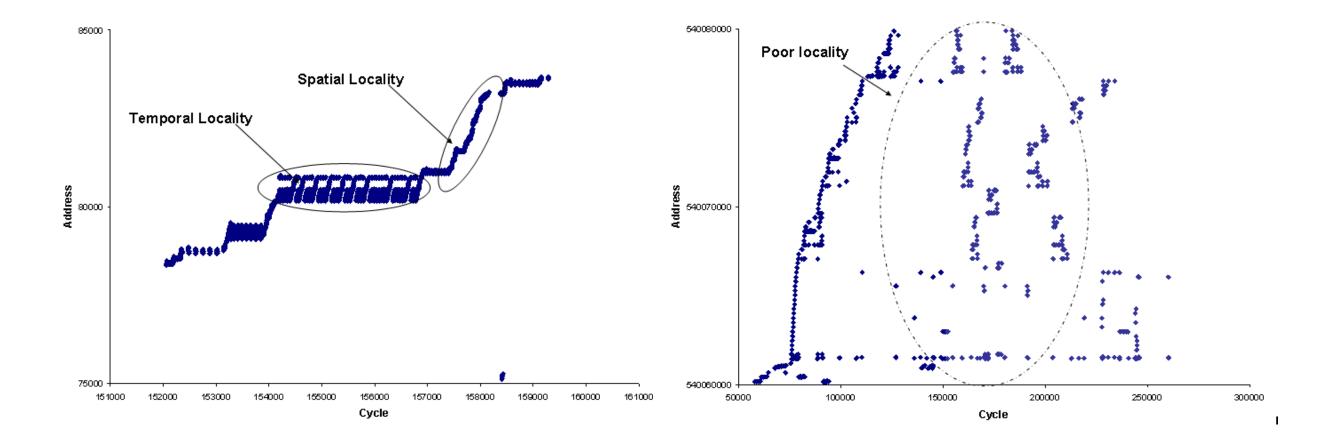

- Coalescing global memory accesses to minimize number of memory transactions

- Improving memory locality of next-stage thread access

- Improving memory locality of inter-thread accesses

Figure 6: Row-major to column-major transformation.

Figure 8: Diagonal strip matrix transposition.

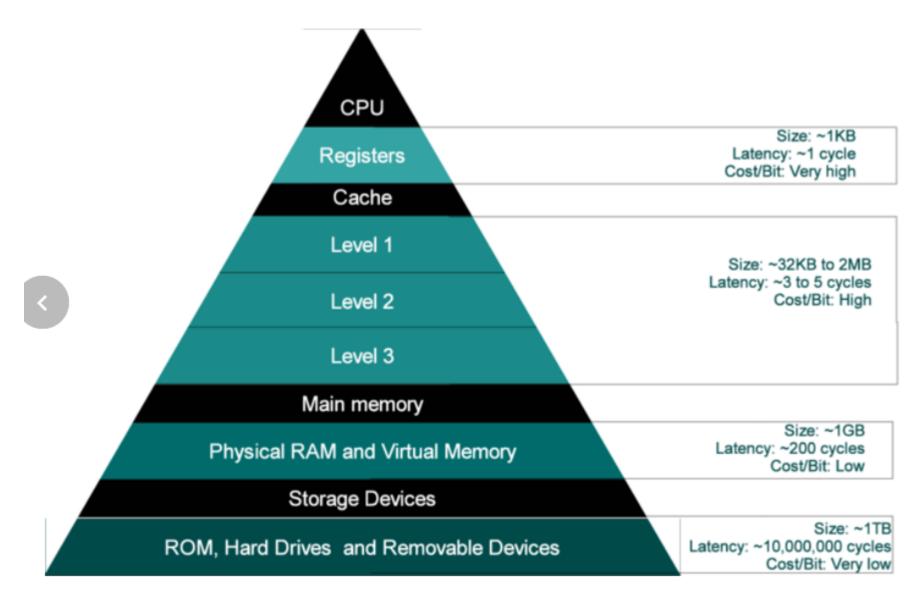

# Memory Hierarchy

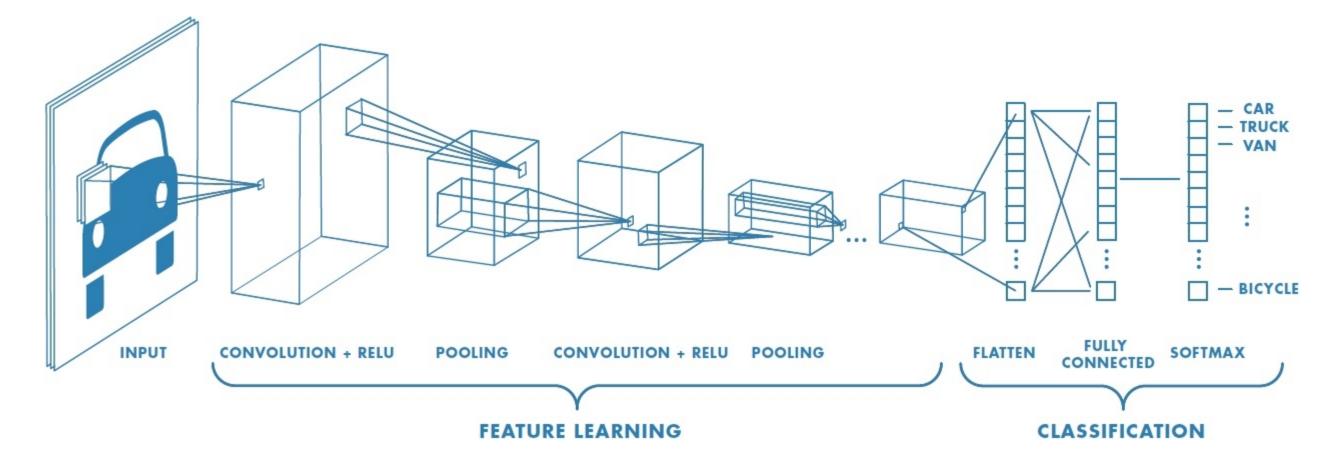

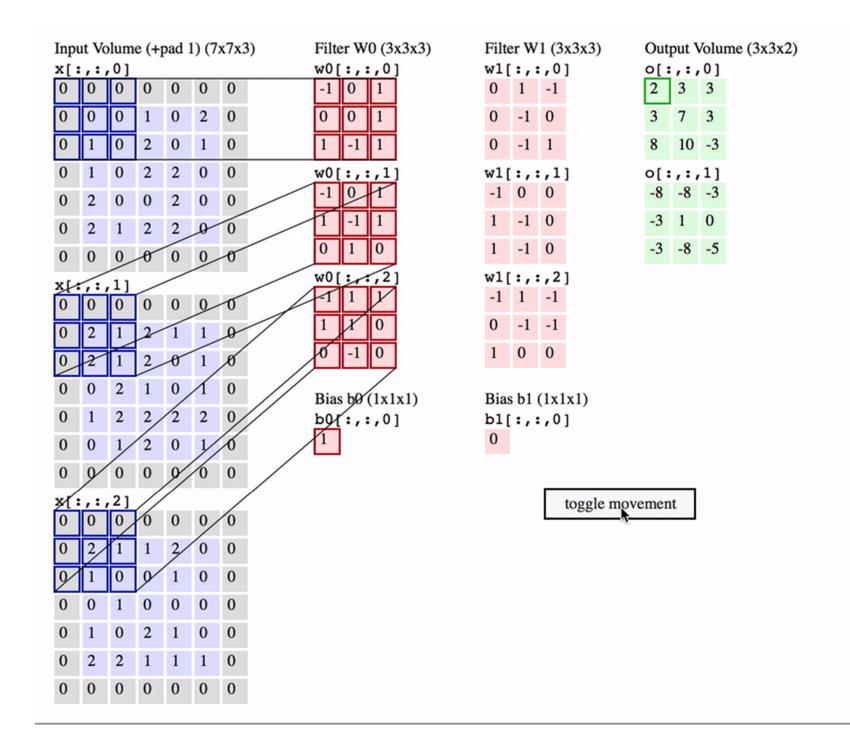

# **Convolutional Neural Network**

https://www.mathworks.com/solutions/deep-learning/convolutional-neural-network.html

#### https://www.embedded.com/print/4017551

#### OpenCL Memory model